| <b>Cache-Conscious Index Structures for Main-Memory Databases</b> |  |  |  |

|-------------------------------------------------------------------|--|--|--|

| Vilho Raatikka                                                    |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

| Helsinki 4th February 2004                                        |  |  |  |

| Master's Thesis                                                   |  |  |  |

| UNIVERSITY OF HELSINKI                                            |  |  |  |

| Department of Computer Science                                    |  |  |  |

|                                                                   |  |  |  |

|                                                                   |  |  |  |

# Faculty of Science Tekijä – Författare – Author Vilho Raatikka Työn nimi – Arbetets titel – Title Cache-Conscious Index Structures for Main-Memory Databases Oppiaine – Läroämne – Subject Computer Science

78 sivua + 4 liitesivua

Aika — Datum — Month and year 4th February 2004

Master's Thesis

Tiivistelmä — Referat — Abstract

Työn laji — Arbetets art — Level

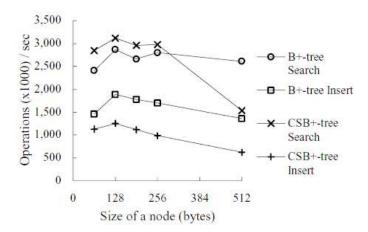

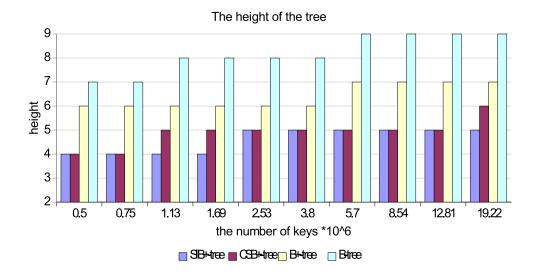

The recent hardware evolution has widened the speed gap between main memory and the processor. As a consequence, in many cases memory access has become the main bottleneck even in disk-based databases. The performance of indices is especially influenced by cache misses; therefore new cache-conscious indices have been proposed. This thesis surveys general methods for enhancing data locality of data structures and how those methods can be applied to database indices. The Cache-Conscious B<sup>+</sup>-tree (CSB<sup>+</sup>-tree) is revisited and formally defined. The worst-case space utilization of the CSB<sup>+</sup>-tree is 25%. Improving the space utilization is one of the main contributions of this thesis. A new, remarkably less-memory-consuming variant of the CSB<sup>+</sup>-tree called the Search-Intensive B<sup>+</sup>-tree (SIB<sup>+</sup>-tree) is presented. The most important cache-conscious index structures are also reviewed and a new, memory saving insertion algorithm is presented. Several methods improving the cache-consciousness of data structures are tested in isolation and as a part of the SIB<sup>+</sup>-tree implementation. The search performance of the SIB<sup>+</sup>-tree is compared with that of the B-tree and the compressed trie. The results show that hardware evolution may be disasterous to data structures with poor data locality such as tries. The cache-conscious search-tree implementation shows the best search performance in all tests.

ACM Computing Classification System (CCS): E.1, H.2.2

Avainsanat — Nyckelord — Keywords

access method, cache consciousness, data locality, data structure, main-memory database

Säilytyspaikka — Förvaringsställe — Where deposited

Muita tietoja — övriga uppgifter — Additional information

# Acknowledgements

This thesis was supervised by Professor Seppo Sippu and Dr. Jan Lindström. I am also thankful for the support I have been given by Ms. Tiina Niklander, PhLic, Professor Kimmo Raatikainen and many other colleagues at the Department of Computer Science. The RTD-Pilot project (ended in March 2002), which was funded by TEKES, Nokia and Solid Information Technology, gave me an opportunity of studying cache-conscious data structures. After the project, this work has been supported by a scholarship from Solid Information Technology. Solid offered me the possibility to work at their office in Helsinki, which gave me the opportunity to participate in many inspiring discussions. The compressed trie implementation used in Chapters 6 and 7 was also offered by Solid.

I would like to thank Dr. Matti Luukkainen and Mr. Tuomo Malinen for their help in modeling the tail recursion in Subsection 3.2.2. I also want to thank Mr. Jarmo Ruuth of Solid Information Technology and Mr. Toni Strandell for the B-tree implementation used in Chapters 6 and 7.

# **Contents**

| 1 | 1 Introduction                               |                                                                 |    |  |  |

|---|----------------------------------------------|-----------------------------------------------------------------|----|--|--|

| 2 | Computer Memory                              |                                                                 |    |  |  |

|   | 2.1                                          | Role of the memory hierarchy                                    | 5  |  |  |

|   | 2.2                                          | Common main-memory and cache types                              | 7  |  |  |

|   | 2.3                                          | Memory access                                                   | 8  |  |  |

|   | 2.4                                          | Principle of locality                                           | 9  |  |  |

|   | 2.5                                          | Cache access                                                    | 10 |  |  |

|   |                                              | 2.5.1 Cache associativity                                       | 11 |  |  |

|   |                                              | 2.5.2 Cache write policies                                      | 13 |  |  |

|   | 2.6                                          | Multilevel caches                                               | 14 |  |  |

|   | 2.7                                          | Virtual memory                                                  | 14 |  |  |

| 3 | Means for Improving Memory Usage             |                                                                 |    |  |  |

|   | 3.1                                          | Amdahl's law                                                    | 16 |  |  |

|   | 3.2 Enhancing data locality of an index node |                                                                 | 17 |  |  |

|   |                                              | 3.2.1 Compressing pointer structures                            | 18 |  |  |

|   |                                              | 3.2.2 An order-preserving compression method for numeric values | 20 |  |  |

|   |                                              | 3.2.3 Comparing uncompressed and compressed node structures     | 22 |  |  |

|   | 3.3                                          | Avoiding conflict misses by relocating data                     | 24 |  |  |

|   | 3.4                                          | Reducing compulsory misses via prefetching                      | 25 |  |  |

| 4 | Cac                                          | he-Conscious Indices                                            | 27 |  |  |

|   | 4.1                                          | Cache-sensitive search tree                                     | 27 |  |  |

|   | 4.2                                          | Cache-sensitive B <sup>+</sup> -tree                            | 29 |  |  |

|   |                                              | 4.2.1 Basic operations on the CSB <sup>+</sup> -tree            | 30 |  |  |

|   |                                              | 4.2.2 CSB <sup>+</sup> -tree variants                           | 31 |  |  |

|   |                                              | 4.2.3 Definition of the full CSB <sup>+</sup> -tree             | 32 |  |  |

|   |                                              | 4.2.4 Height of a full CSB <sup>+</sup> -tree                   | 33 |  |  |

|   |                                              | 4.2.5 Cost of search and insert operations                      | 34 |  |  |

|   | 4.3                                          | Concurrency control over a CSB <sup>+</sup> -tree               | 35 |  |  |

| 5 | Sear                                         | rch-Intensive B <sup>+</sup> -tree                              | 37 |  |  |

| 1 | V |

|---|---|

| References                              |                         |               |                                                                             |    |  |

|-----------------------------------------|-------------------------|---------------|-----------------------------------------------------------------------------|----|--|

| 8                                       | Con                     | clusions      | S                                                                           | 70 |  |

|                                         |                         | 7.3.4         | Sequential search test                                                      | 68 |  |

|                                         |                         | 7.3.3         | Random search tests                                                         | 66 |  |

|                                         |                         | 7.3.2         | Determining the node size by calculating cache look-ups                     | 64 |  |

|                                         |                         | 7.3.1         | Test settings                                                               | 63 |  |

|                                         | 7.3                     | Search        | performance of the SIB <sup>+</sup> -tree implementation                    | 63 |  |

|                                         |                         | 7.2.4         | Traverse test on clearly different platforms                                | 61 |  |

|                                         |                         | 7.2.3         | Traverse test with four computers equipped with P4 processors               | 60 |  |

|                                         |                         | 7.2.2         | Traverse test with variable-size structures                                 | 59 |  |

|                                         |                         | 7.2.1         | Test settings                                                               | 58 |  |

|                                         |                         |               | g the traversal speed of cache-conscious and $B^+$ -node structures $\ \ .$ | 56 |  |

|                                         | 7.1                     | Hardw         | vare settings                                                               | 55 |  |

| 7                                       | Experimental Evaluation |               |                                                                             |    |  |

|                                         | 6.4                     | Achiev        | ved code optimizations                                                      | 52 |  |

|                                         | 6.3                     | Profili       | ng and analyzing the code                                                   | 50 |  |

|                                         | 6.2                     | Group         | -splitting policy                                                           | 50 |  |

|                                         | 6.1                     | Structu       | are                                                                         | 48 |  |

| 6 SIB <sup>+</sup> -tree Implementation |                         | mplementation | 48                                                                          |    |  |

|                                         |                         | 5.6.4         | Memory usage analysis                                                       | 46 |  |

|                                         |                         | 5.6.3         | Leaf-node-group utilization                                                 | 45 |  |

|                                         |                         | 5.6.2         | Cost of the SD algorithm                                                    | 44 |  |

|                                         |                         | 5.6.1         | Description of the Split-Delay algorithm                                    | 42 |  |

|                                         | 5.6                     | -             | Delay insert algorithm of the SIB <sup>+</sup> -tree                        | 42 |  |

|                                         | 5.5                     |               |                                                                             | 41 |  |

|                                         | 5.4                     |               | bulk-load algorithm                                                         | 40 |  |

|                                         | 5.3                     |               | look-ups caused by a tree traversal                                         |    |  |

|                                         | 5.2                     |               | t of a SIB <sup>+</sup> -tree                                               |    |  |

|                                         | 5.1                     |               | tion of the SIB <sup>+</sup> -tree                                          |    |  |

|                                         |                         |               |                                                                             | _  |  |

Appendices

- 1 Bit operations used while mapping a memory address to a cache line

- 2 Search within a compressed node

- 3 Search algorithm for the  $CSB^+$ -tree

# 1 Introduction

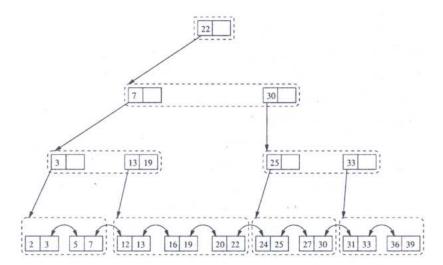

Database index structures have been researched for decades. Disk databases use hard disks as primary non-volatile storage and the main issue is to keep the number of disk operations as low as possible. This is due to the fact that disk access is magnitudes slower than main-memory access. By offering the shortest possible path to data, indices can substantially reduce the need for disk operations. This has led to the popularity of low, bushy tree-structures. In a B<sup>+</sup>-tree [Com79, Sag86], for instance, the node fanout, i.e., the number of children per node, is high. The B<sup>+</sup>-tree suits well for disk databases and is the most common index structure used.

Since relatively large main memories became available in the mid 1980's, partially or fully memory resident databases became feasible [DKO+84, GMS92, JLR+94, CPP97, DKK99, BBG+99, LNPR99]. This evolution also motivated the research of index structures especially designed for main-memory databases (*MMDB*). The properties and needs of MMDB indices differ from those of traditional disk-based databases. Although the aim of the design of MMDBs is the efficient use of processor cycles as well, the emphasis has been on minimizing the stress of the CPU rather than optimizing the usage of the cache.

For over two decades the speed of CPUs has increased faster than the speed of main memory. As a consequence, the speed gap between the CPU and memory has rapidly become steeper, and memory access has become the new bottleneck in databases [RBH<sup>+</sup>95, Pat97, CHL99, BKM99, ADHW99, BDFC00, PH02]. Therefore, it is crucial to minimize both the number of memory accesses the application causes and the latency incurred from the memory accesses. The performance of the CPU should not be the problem anymore in data-intensive programs. The target of this thesis, in general, is to explore the methods which enhance the cache usage of index structures of totally memory-resident databases.

The B<sup>+</sup>-tree has many benefits over binary trees, such as short access paths with equal length. However, these benefits lose their importance if memory access is relatively fast as it was in the mid 1980's [LC86b, GMS92]. DeWitt et al. showed in 1984, that if at least 80% of the database data resides in main memory, an AVL-tree, or any balanced binary tree outperforms a B-tree [DKO<sup>+</sup>84]. As a consequence binary trees became widely used in main-memory databases. At the time the T-tree [LC86a] was proposed, memory access was not yet the primary bottleneck in databases as it is today. Instead, the aim of the design was to strain the CPU with as simple and few instructions as possible. Thus, the efficient CPU-cycle usage materialized with a T-tree. It enhances the poor storage properties of the AVL-tree, still retaining the binary structure. Unlike the nodes of an AVL-tree, each T-tree node has multiple elements, thus reducing the need for rotations typical to balanced binary trees. The original T-tree has data items in each node. To achieve better scanning properties, some variants of the T-tree have been proposed. In a T<sup>+</sup>-tree [LC86a] data is stored only on leaf nodes as in a B<sup>+</sup>-tree. In a T<sup>2</sup>-tree [JKN<sup>+</sup>01], the leaf nodes are also linked in order to allow sequential access from leaf to leaf. For over ten years, different variations of the T-tree have been widely used in existing MMDB products.

Optimizing the main-memory and cache usage is topical due to the increase in the memoryprocessor speed gap. This issue has come up quite recently and nearly all MMDB products rely on solutions based on outdated or too optimistic ideas about main-memory performance. A property called data locality (or reference locality) relates to how mostfrequently-referred-to data is placed into the memory [CHL99, PH02, Ch.1.6]. Arrays inherently expose good data locality while pointer structures usually do not. The relative retardation of main memory is disastrous for pointer-based binary trees, which typically expose bad reference locality. Despite of the efficient search properties of binary trees, the increased cost of memory access makes them inefficient. As a consequence of this long-term hardware evolution, the B<sup>+</sup>-tree, surprisingly, has been shown to perform better on modern hardware than the T-tree [LNT00]. Regardless of the relatively good performance of the B<sup>+</sup>-tree, many of its properties, such as data locality, can be enhanced in many ways. Within the past few years many cache-conscious data structures, programming conventions and design issues have been proposed [ADHW99, BKM99, CHL99, Leb99, RR99, RR00, Gra01, ZR02, ZR03]. Cache efficiency can be improved both by a careful design and an efficient implementation. Both aspects will be examined in this thesis. However, this thesis covers only the software enhancements, thus, hardware issues are not discussed.

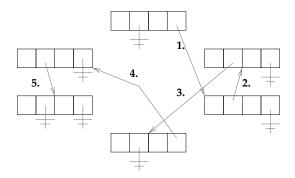

Two methods, coloring and clustering have been proposed to enhance the reference locality of programs [CHL99]. Assume two consecutively accessed elements, both in size equal to the cache block. Coloring is used to allocate these elements to such memory addresses that they will not conflict in cache. That is, they can both be in the cache at the same time. Coloring materializes with explicit memory management which aims at non-conflicting data placement. Clustering attempts to store consecutively-accessed elements into a same cache block. Clustering is the main idea in the Cache-Conscious Search tree (CSS-Tree) [RR99]. It performs well in searches but supports updates poorly. The structure of the CSS-tree consists of arrays; like virtually all sorted arrays, when a write operation occurs, large parts of the array must be re-written. When a write occurs, the whole tree must be re-created. Clustering also materializes in proposed cache-conscious variants of the B<sup>+</sup>-tree, called CSB<sup>+</sup>-trees. They support read and write operations, but locking and concurrency-control schemes are not discussed [RR00]. An optimistic, latchfree traversal (OLFIT) concurrency-control scheme for multiprocessor systems has been implemented on a tree which resembles the CSB<sup>+</sup>-tree [CGM01]. Read and update algorithms are described; delete operations are achieved by a well-known versioning scheme [BLR<sup>+</sup>95]. Data prefetching is an efficient method to amortize memory-access cost while accessing consecutive blocks from the main memory [CGM01, CGMV02]. Prefetching reads data items which are to be accessed soon, beforehand into the cache, asynchronously with program execution. The theoretical "cache-oblivious search-tree" is a tree structure that performs well with multiple levels of memory [BDFC00]. The solution conforms to a weight-balanced B-tree [AV96]; it is independent of the memory levels, block sizes, number of blocks on each level, and the speed of memory access.

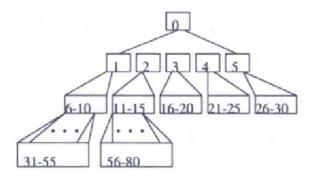

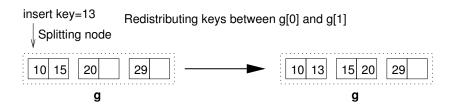

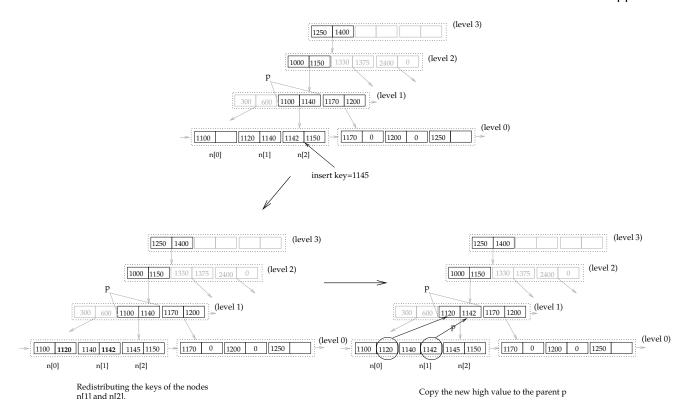

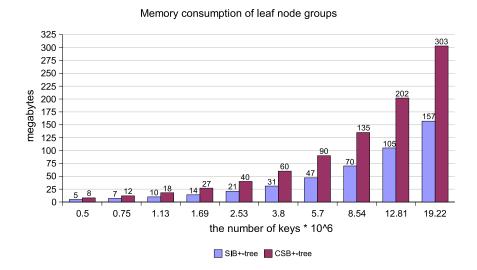

A *full CSB*<sup>+</sup>-tree is a variant of the CSB<sup>+</sup>-tree [RR00]. In the full CSB<sup>+</sup>-tree the nodes are stored in constant-size node groups. A node group is actually an array of nodes containing keys and pointers. Arrays are used to eliminate pointers from nodes, thus increasing both the node fanout and reference locality. Eliminating pointers requires physical grouping of nodes. Unfortunately, this may remarkably increase the memory overhead. As in B<sup>+</sup>-trees, the minimum node utilization (i.e, space utilization within a node) in the CSB<sup>+</sup>-tree is 50%. However, the minimum node-group utilization, the number of nodes present against the maximum number of nodes a node group can have, is also 50%. In other words, any node group is at least half-full and so are all the nodes. Thus, the minimum overall utilization in the CSB<sup>+</sup>-tree is only 25%, which can be disastrous to the performance of the structure. This issue is noticed in [RR00], but the focus is on decreasing the memory usage of internal nodes because they are more relevant when the cache usage is considered. The total memory usage, which depends on the number of leaf-node groups, is also important when the amount of memory is limited.

We propose a variant of the CSB<sup>+</sup>-tree, called the *search-intensive* B<sup>+</sup>-tree (SIB<sup>+</sup>-tree), which guarantees at least 50% memory utilization on the leaf level of the SIB<sup>+</sup>-tree. In other words, the worst-case memory usage of the SIB<sup>+</sup>-tree is half of that of the CSB<sup>+</sup>-tree. The enhancement is due to the proposed *split-delay insert* algorithm (SD algorithm), which delays the splitting of a full leaf-node group until all the nodes are full. The formal definitions for the CSB<sup>+</sup>-tree and for the SIB<sup>+</sup>-tree are presented. We also define an order-preserving compression method, called the *difference* compression method, which in many cases multiplies the number of keys a node can contain. Finally we investigate several methods for search within a node (of the CSB<sup>+</sup>-tree) and propose a method which combines binary search and sequential scan in the most efficient way.

The SIB<sup>+</sup>-tree was implemented with the SD algorithm and with an optimized node search, its memory usage and cache behaviour were compared to those of a B-tree and of a compressed trie [INT99, Sed98, Ch.15]. The search performances of the SIB<sup>+</sup>-tree, the B-tree and the compressed trie were thoroughly tested on several machines with varying properties. The test results of different indices are compared against each other and profoundly analyzed. The analysis is based both on the properties of the structures and on the properties of the hardware used. The difference-compression method was tested on several machines with different properties. The test results are compared to those of the uncompressed storing method. The results of the comparison are presented and analyzed. Two linked-list-like data structures, called the B<sup>+</sup>-chain and cache-conscious chain (CC-chain) were implemented in order to explore the performance of CPU-efficient and memory-efficient data structures. The chains were tested on several machines with varying properties. The results for both chains are compared and profoundly analyzed.

The remaining part of the thesis is organized as follows. The main principles of computer memory are surveyed in Chapter 2. The different ways to enhance memory usage are discussed in Chapter 3. Cache-sensitive index structures are reviewed in Chapter 4. The definition of the SIB<sup>+</sup>-tree is presented in Chapter 5. The operations implemented and

the details of the implementation are presented in Chapter 6. The tests and results are documented in Chapter 7, and Chapter 8 concludes the thesis.

# **2** Computer Memory

It would be desirable to have an unlimited amount of memory, so that any word would instantly be available for processing. "Unlimited" means that one does not need to worry about the adequacy of storage regardless of the number and the size of the programs one uses. An "instant" access means that memory must be able to feed the processor with data without delaying the CPU.

Consider a computer with a processor running at a clock rate of 1,5GHz, a 40GB hard disk, 512MB main memory and 384 kilobytes of cache. The total size of the memory is tens of gigabytes, which can be considered "infinite". Furthermore, we can always add one or two additional hard disks to our computer in order to multiply the overall storage capacity. However, the data on the disk is not immediately available. It must be transferred to the processor via main memory and cache before use. Thus, the amount of memory the computer includes is sufficient but the speed of the memory is mostly too slow.

# 2.1 Role of the memory hierarchy

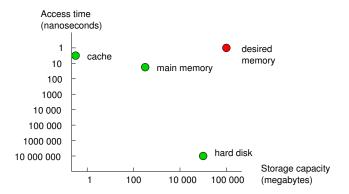

In an above described computer only the smallest and fastest part of the memory hierarchy meets the requirements of "instant access". In other words, 0,001% of the memory (the cache) is fast enough while 98,7% is millions of times slower than desired. The remaining part consists of moderately fast main memory holding a 1,3% share of the total memory size. Therefore, user expectations often collide with the reality as can be seen from Figure 1. One reason for the situation is an economical one. The cost of a megabyte varies greatly between the different memories. If it were possible for manufacturers to produce small and "fast enough" memory chips, they would be far too expensive for consumers. Currently hard disk is the only non-volatile storage type in computers. Therefore, it cannot be replaced by large volatile main memory.

Figure 1: The speeds and sizes of different memories.

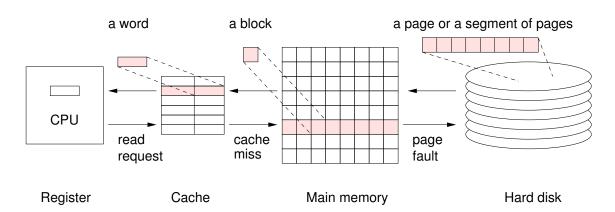

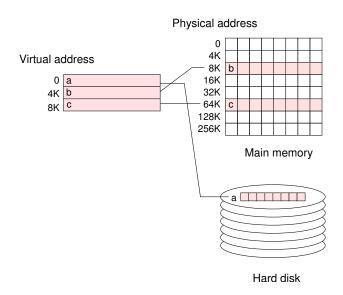

The different types of computer memory constitute a multilevel *memory hierarchy* (see Figure 2). On the top of the hierarchy are processor registers and the cache, which both are located on the CPU chip. The size of the registers is only a few words while the size of the cache is 32 to 2048 kilobytes. The second level of memory consists of main memory. The main memory is placed on the memory bus of the motherboard and its size varies from 128MB to a few gigabytes. Finally, at the bottom of the memory hierarchy there is the hard disk, whose size is typically dozens of gigabytes. Motivation for this kind of a hierarchy is the user's need for a fast memory with large enough capacity. Such a facility cannot be offered, but it can be simulated to some extent with a set of different, co-operating memories using the principle of locality (or reference locality) [Leb99, CHL99]. Assuming that only a small portion of data will be heavily accessed, it is enough to keep this "hot" data quickly available in cache and store other data to memory or to disk.

Generally, every computer has one non-volatile storage device which usually is a hard disk. All data is stored on hard disk, from where the requested parts of the data are copied to the processor via main memory and cache. If the data needed can mainly be found from the cache or from the main memory, the user shares the illusion of having large amounts of moderately fast memory always available. In order to successfully create such an impression, the memory management of the computer must recognize the most frequently used data and keep it as close to the CPU as possible (i.e. on highest possible memory level) by using of the memory hierarchy. The data found on one level of the hierarchy is actually a subset of the data found on the next lower level (see Figure 2).

Figure 2: Data request through the hierarchy. Participants and units of transfer.

Data is transferred between memory levels in blocks. The transfer block between hard disk and main memory is a page or a segment. The segment usually consists of multiple pages. The size of a page varies typically between 4 and 64 KB. Data is transferred from the main memory to the cache in blocks equal to the size of the *cache line*, which is the basic addressing unit in cache. The size of a cache line is usually 16-128 bytes. The CPU reads data in one-word pieces; the word size depends on the processor architecture used (16 bits in 8086 and 64 bits in Intel Pentiums).

In data-centric programs the processor spends most of its execution time by waiting data to come from the bus. That determines the main challenges in designing an efficient data structure: avoid cache misses and thus minimize the CPU's stall cycles resulting from memory references. The situation is slightly alleviated by processors including non-blocking caches, which in some cases can continue processing while waiting for the data from the cache [CB92][PH02, Ch.5.6]. However, this works only as long as the CPU has data to process, thus being only a minor enhancement.

# 2.2 Common main-memory and cache types

Every computer includes a memory controller that creates and manages signals needed in reading and writing information from and to the memory. The main signals are control, address and data signals. A control signal tells the memory the type of the operation, and an address signal tells the memory the location of the cell where the operation should be executed. Data signals are used to transfer data to and from the memory. The memory controller is usually integrated into the system chip set.

The most familiar types of memories used in desktop computers and servers are the dynamic RAM (DRAM) and static RAM (SRAM). The main memory constitutes usually of some type of DRAM. Similarly, the cache is nearly always made of SRAM, regardless of whether it is internal or external to the CPU. Main memory consists physically of a set of DRAM chips. Chips are grouped and attached to a piece of silicon that is connected to memory slots of the main board. Data flows from memory via connector pins.

DRAM is called dynamic because it must be refreshed frequently to retain its contents. DRAM has only one transistor per bit and one capacitor, while SRAM has at least six transistors. The capacitor holds or releases an electrical charge to express '1' or '0', respectively. The transistor is used to read the content of the capacitor. The capacitors are very small and they hold the charge only for a short time before it fades away. This is why refreshing is needed: each cell must be read before it loses its information. The reading is done by a particular refresh circuit that reads the content of each memory cell. The refresh circuitry is part of the memory controller. Refreshing must be done periodically, regardless of the actual need for accessing data. The memory is also refreshed as a side effect when data is read.

In theory, if 32-bit addressing is used, the memory needs 32 address lines to manage the addresses. In order to save space, DRAM address lines are multiplexed. The main memory constitutes logically a square of rows and columns. The address is divided into two parts, row address and column address, which are sent through the same connector pins one after another. This slows the DRAM further, but it also halves the number of address lines and saves valuable space.

The capacity of main memory has increased very fast, but the speed of DRAM has increased much slower than the speed of the CPU. As the size of memory has grown over 50% per year, the speed of memory has increased only about 5% per year. The *row access strobe* (RAS), which is related to latency, of fast DRAMs has decreased from 150ns (1980) to 40ns (2002) in 22 years [PH02, Ch.5.9].

Unlike the DRAM (main memory), the evolution of the SRAM (cache) has followed tightly the evolution of the CPU. Fetching data from the cache takes only one clock cycle. Depending on the CPU, the cache latency is 4 to 10 nanoseconds. SRAM differs from DRAM in (at least) three things:

- 1. SRAM does not need to be refreshed in order to preserve its contents. Therefore, SRAM needs less power than DRAM.

- 2. As opposite to DRAM, SRAM address lines are not multiplexed. Thus, SRAM needs twice as many connector pins as DRAM, but addressing is faster because the whole address can be received during the same clock cycle.

- 3. Cache is integrated with CPU, therefore the cache runs at the clock rate of the CPU making the few nanoseconds access time possible.

As a consequence, SRAM is much more expensive than DRAM. One-megabyte SRAM module costs 86,5 euros [Dat02] while the price of the same amount of DRAM is 0,3 euros [Ver02]. SRAM thus costs nearly 300 times more than DRAM. This is, of course, partially due to manufacturing volumes. In comparable technologies, SRAM is 8 to 16 times as expensive as DRAM [PH02, Ch.5.9]. By way of comparison, one megabyte of hard-disk costs 0,002 euros [Ver02].

# 2.3 Memory access

When a program is being executed, each instruction and required data item is generally retrieved from the memory. The memory reference (to access data or an instruction) starts with requesting the intended bytes from the cache. Because each process uses a dedicated virtual-memory address space, the *virtual address* must first be translated into a *physical address*. This is done by extracting the virtual page number from the virtual address and then translating the virtual page number to the physical page number. The remainder of the virtual address, an offset, is then concatenated to the physical page in order to form the physical address.

The physical address is sent to the cache. If the data is found, a *cache hit* occurs and the data is copied to the registers of the processor, which continues the execution. If the data cannot be found in the cache, a *cache miss* occurs. As a consequence, the processor stalls and the data is searched from the main memory and, if found, copied to the cache. If the page cannot be found in the memory, a page fault occurs and the CPU invokes the

operating system by using an exception. As a consequence, the page is read from the disk to the main memory and forwarded to the cache. When the data is available in the cache, the CPU continues the execution from the point it was stalled by redoing the memory reference to the cache. Since the focus of this thesis covers the problems arising from the relatively slow memory references originating from cache misses, further examination of lower-level memories such as hard disks or network file systems, is beyond the scope of the thesis.

Cache misses in a uniprocessor system can be divided to three distinct types [PH02, Ch.5.5]:

- 1 A compulsory miss occurs at the first time the data is referenced.

- 2 A capacity miss occurs when the size of the data to be read exceeds the cache capacity.

- 3 *A conflict miss* is a consequence of the cache's limited associativity. Data can be stored to a limited set of cache blocks. A conflict miss means that the missing data was replaced by another block, whose memory address is mapped to the same set of cache lines than the address of the replaced data.

Compulsory misses can be reduced, for instance, by using a *prefetch* mechanism [CB92, CGM01, PH02, Ch.5.6]. Capacity misses can be avoided by increasing the physical size of the cache or by diminishing the program's cache footprint. Coloring [CHL99], in turn, can be used to reduce conflict misses. Coloring and prefetching are studied briefly in Sections 3.3 and 3.4, respectively.

A shared-memory multiprocessor system is one possibility for a parallel computing environment. In such an environment an additional type of cache miss, called *a coherence cache miss* exists. The coherence cache miss occurs when many processors have cached a block at the same time and one writes it. As a consequence, the block written is invalidated in the caches of the other processors. A cache miss occurs when the other processors try to access the block written. The effect is multiplied if processors repeatedly access the same cache block.

# 2.4 Principle of locality

The principle of locality is an important property for program efficiency [PH02, BO03, Ch.1.6, Ch.6.2]. It states that if a program uses a piece of code once, it is likely to use the same code again soon. A common rule says that a program spends 90% of its execution time in using only 10% of the code. The principle of locality means that it is possible to predict what instructions a program will use in the future based on its usage in the recent past. The principle of locality also applies to data access, but not as strongly as to code access. Depending on the data access pattern, two kinds of locality have been defined.

*Temporal locality* means that if a piece of data has been accessed recently, it will likely be accessed again soon. *Spatial locality* states that two data items, which are physically close to each other, tend both to be accessed in a short period of time.

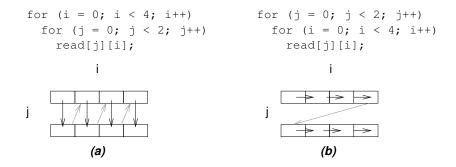

Data structures can roughly be divided into two categories, arrays and pointer structures. In an array, subsequent data items are physically side by side. The reference locality of an array can be improved by rearranging the data access pattern. In Figure 3, a 2x4 matrix, whose line size equals to cache line size, is accessed. With access pattern (a), every access may result in a cache miss. If two cache lines are mapped to the same set in the cache, they may replace each other every time they are copied to the cache. With access pattern (b), the number of cache misses is minimized. The spatial locality of arrays may also be improved by using some compression method. The effect of compressing internal structure of index nodes is examined in Section 3.2.

Figure 3: Improving spatial locality by rearranging the data access pattern.

Pointer structures have a property called *location transparency*, which is generally a powerful feature. It allows changing data placement without changing the semantics of a program. This may sometimes lead to poor reference locality. Subsequently accessed items in a pointer structure are seldom physically side by side as in an array. As a consequence, subsequent items can reside in different cache lines. It is also possible that the next-to-be-processed item for a recently processed item is currently placed on the disk. Furthermore, the access pattern of a pointer structure, such as a B<sup>+</sup>-tree, usually cannot be changed. Thus, methods for enhancing locality that apply to arrays will usually not work with pointer structures. However, the cache usage of a pointer structure can still be improved by shortening the data-access path or replacing certain, often-accessed parts of the structure by arrays. The latter is sometimes called *pointer-structure compression*. It is studied further in Subsection 3.2.1.

### 2.5 Cache access

The cache consists of fixed-size blocks, cache lines. Each cache line has three types of components: a *tag field*, a *valid bit*, and one or more *data fields*, each being equal in size with a word. The valid bit indicates whether or not the tag field includes a proper

memory address. It is set when the cache line is filled with data. There is also an *index field* associated with every group of cache lines which are mapped to the same memory address. Those groups are called *cache sets* and they relate to cache associativity (Subsection 2.5.1). The index fields are used to locate the correct cache line among the cache lines. The value of the index field is called also the *cache line number*. One possible way to achieve the bit operations needed in address mapping is presented in Appendix 1.

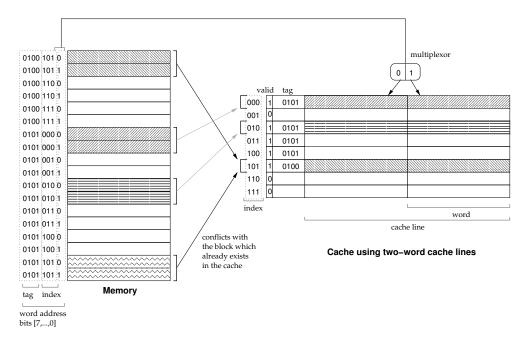

Figure 4: A direct-mapped cache using two-word (2 bytes each) cache lines. Bit 0 of word address (the rightmost) addresses the word inside the cache line, bits 1-3 determine the cache line number (the index value), and bits 4–7 identify the word(s) inside the cache line (the tag value).

### 2.5.1 Cache associativity

When the CPU sends an address of a data item to the cache, the address is mapped to one or more cache lines in the cache. The mapping depends on the way the address associates with the cache lines, thus it is dominated by the cache type. Caches facilitate different mappings; from those in which each memory address is mapped to exactly one cache line, to those in which any memory address can be mapped to any cache line. Caches applying the former mapping, as in Figure 4, are called *direct mapping caches*. Caches that allow a single address to be mapped to any cache line are called *fully associative caches*. Between these two is the most typical model in which one main-memory address can be mapped into two or more cache lines. This kind of a cache is called a *set-associative cache*. Generally, if a single memory address can be mapped to *n* cache lines, it is called an *n-way set-associative* cache.

The terms to be used in address mapping are defined as follows. A *byte address* is a bit string that uniquely addresses a byte from the memory. A *word address* is a bit string that uniquely addresses a word from the memory. A *cache line address* is a subset of a byte address which is used to determine the cache lines(s) the byte address is mapped to.

Mapping a memory address to a cache line in a direct-mapped cache is performed as follows:

```

word address = (byte address) div (bytes per word)

cache-line address = (word address) div (words per cache line)

```

By using these definitions, the cache line number (the index value) is resolved as follows:

```

cache-line number = (cache-line address) modulo (number of cache lines)

```

For example, the word address of byte address 010010110 or 010010111 is 01001011, if there are two bytes per word. Similarly the cache-line address of word address 01001011 (as well as for 01001010) is 0100101, if the cache uses two-word cache lines. Finally, the word in address 01001011 is mapped to the cache line attached with number 101, if the number of cache lines in the cache is 8 and 0100101 modulo 8 = 101.

Mapping to an *n-way set-associative* cache differs only a little from the method used in a direct-mapped cache. While in a direct-mapped cache the number of different mapping targets is same as the number of cache lines, one address maps to exactly one cache line, in an *n*-way set-associative cache there are

$$number\ of\ sets\ in\ cache = \frac{number\ of\ cache\ lines}{n}$$

possible targets, that is, sets for mapping. The cache-line address is calculated as in a direct-mapped cache, but since there are multiple cache lines whereto a memory block may be mapped the cache lines address is divided by the number of sets instead of the number of cache lines. A memory address is mapped to an *n*-way set-associative cache as follows:

```

cache-line number = (cache line address) modulo (number of sets in the cache)

```

Reading a word from a direct-mapped ("1-way set-associative") cache is simple: the memory address needs only to be mapped to a cache line, and if the valid bit is set, the word found from the cache line is sent to the CPU registers. In a 2-way set-associative cache the address maps to a slot that includes two cache lines. In order to find the right word, both of the cache lines may have to be inspected (if the first does not match). This is performed by looking at the tag field of both cache lines. The matching tag field indicates a cache hit. Reading data from an *n*-way set-associative cache begins with searching the matching index field, that is, the correct set for the data. After locating the correct set, at most *n* tag fields must be inspected in order to find the searched word. In a fully associated cache all tags of the cache lines of the cache may have to be read, because all cache lines belong to the same set. Fully associated caches are rare and when one exists it is usually very small in order to be efficient [PH97, Ch.7.3].

### 2.5.2 Cache write policies

Writing the data only to the cache, but not to the memory, or vice versa, could result in a situation where the contents of the cache differ from the contents of the memory. That is, the cache and the memory may be in an inconsistent state. Therefore, the requirement for all write strategies is to keep the memory and the cache consistent as well as to achieve sufficient performance. A simple method to retain consistency is to write everything to the memory immediately after it is written to the cache. This method is called *write-through*. In a direct-mapped cache the updated value can be written straight to the cache without trying to read it first. In a set-associated cache the old value must be located (among cache lines in the same set) and replaced with the new value. If the data which is to be written is not in the (set-associated) cache, a *write miss* occurs. A write miss is managed by first selecting the cache line for the data, and then the updated value is written to the selected cache line as well as to the memory.

Write-through is not a very efficient solution since it causes writing both the cache and the memory on each write operation. In practice, write operations do not benefit from the existence of a cache in the write-through scheme because the CPU is stalled during the write. When the processor waits the write to complete, a *write stall* takes place. The impact of a write stall may be alleviated by using a *write buffer* to which the data is written instead of the main memory. The data in the write buffer is written to the memory simultaneously thus allowing the CPU to continue its execution. If the write buffer is full, the CPU stalls until a slot is freed in the buffer. A slot of the write buffer is freed only when some data is written from it to the memory.

An alternative write scheme is *write-back*, which operates only to the cache during a write. Thus, the time needed for a write is much shorter than when also the main memory must be accessed. The updated cache-line content is written to memory only when the cache line is to be replaced by some data. Write-back is effective especially when the same value is rewritten multiple times, because of multiple memory accesses are avoided. If the content of the cache line is updated, the *dirty bit* attached to a cache line is set. When a cache line is to be replaced by another cache line, the dirty bit determines whether or not the data needs to be written to memory.

In general, write-back is more efficient than write-through; especially when writes are bursty and memory referencing would stall the CPU for a long time. On the other hand, implementing the write-back scheme is more complicated than the write-through scheme [PH97, Ch.7.3][PH02, Ch.5.2].

In set-associative caches some *block-selection strategy* must be used to determine which cache block (*a victim block*) must be replaced when new data arrives. Some possible strategies are: first-in-first-out (FIFO), least-recently-used (LRU), or random. In the case of FIFO, the oldest line among the cache lines in the set is overwritten. If LRU is used,

the line which is the oldest untouched is replaced.

### 2.6 Multilevel caches

Modern computers usually include a *first-level cache* (L1 cache) internal to the CPU and a *second-level cache* (L2 cache) external to the CPU. The L1 cache is typically 16–256 kilobytes while the size of the L2 cache may be up to four megabytes. Since the L1 cache is attached to the CPU it is synchronized with the CPU clock. It cooperates with the processor so that the CPU will not starve. The L2 cache is located on the data bus, but very close to the CPU. As the L1 cache, the L2 cache consists of a set of SRAM chip(s). It is slower than the L1 cache, but requesting data from it is still remarkably faster than from the main memory.

The L2 cache usually decreases the overall cache-miss rate. Since memory access requires checking two levels (1 and 2) of the cache, using L2 also increases the total cache-miss latency. If the L2 cache exists, the L1 cache is checked as described earlier, but in the case of an L1 cache miss the L2 cache is checked instead of the main memory. If the requested data is found in the L2 cache it is copied both to the L1 cache and to the CPU. When an L2 cache miss occurs the main memory is accessed.

Suppose we have a processor that does one instruction in one clock cycle (CPI=1) with an L1 cache hit and a clock rate of 500 MHz. Suppose further that the access time for the main memory is 200ns and for the L2 cache 20ns. The L1 cache-miss rate is 5% and with L2 cache the overall miss rate is 2%. The miss penalty for the main memory is 100 clock cycles and for the L2 cache 10 clock cycles. Therefore, the average CPI without the L2 cache is 1 + 5% \* 100 = 6 and with the L2 cache 1 + 5% \* 10 + 2% \* 100 = 3.5. Thus, the computer is 1.7 times faster with the L2 cache than without it.

# 2.7 Virtual memory

The main memory can be seen as a layer between the cache and the hard disk. It is accessed as a consequence of a cache miss or a write. Furthermore it acts as the I/O interface for the rest of the system.

In our example computer the fraction of main memory out of the total amount of memory is 1.3% while that of hard disk is over 98%. To create an illusion of a single flat memory, a mechanism called *virtual memory* is used. The virtual memory wraps the two memory layers below the cache to look like a single memory. Virtual memory frees programmers from worrying about things like how to make an application fit entirely into memory or what particular parts of a program must be loaded at a certain step of execution. A program in execution and the data it uses always seem to be in memory in their entirety, although only some of the virtual addresses may simultaneously be mapped to

main memory while the rest are mapped to hard disk, as shown in Figure 5. Each process is given a dedicated and contiguous logical memory address space. Furthermore, the virtual memory restricts each process to its own memory area so that processes cannot disturb each other.

Figure 5: Mapping a logical memory area to physical memory.

When data is to be read from memory the process submits a virtual address consisting of a virtual page number and a page offset. The virtual address is translated to a physical address by means of a page table. The page table contains the physical page addresses and it is indexed by the virtual page numbers. The virtual page number is mapped to a physical page address and the page offset is added to it.

The page table itself may be stored in main memory and can also be paged. In such a case the cost of each memory reference may be doubled. In order to avoid this extra cost, an additional cache for page mapping is used. This special cache is a *translation look-aside buffer* (TLB). Instead of using the page table the virtual address is first searched from the TLB. If it is found, a *TLB hit* occurs and corresponding physical page number is retrieved. Otherwise a *TLB miss* occurs and the physical page number must be obtained from the page table.

As in memory caches, according to the principle of locality, only a small number of the memory pages are usually accessed. Thus, when storing recently translated addresses to TLB, most address translations do not need to access the page table. TLB is quite similar to a memory cache. TLB entries have generally a tag and a data portion, which hold a virtual page number and a referring physical page number, respectively. In addition, a TLB entry usually contains a dirty bit and a valid bit. The dirty bit is set when the physical page is dirty, that is, updated. The valid bit is used in the same way as with caches.

# **3** Means for Improving Memory Usage

Memory accesses based on poor data locality may reduce substantially the performance of a program. The locality can be improved by careful design of data structures and algorithms. Modern processors also offer functionalities such as non-blocking caches or prefetching, which alleviate the main memory bottleneck.

### 3.1 Amdahl's law

An enhancement in one part of a computer results in improved processing. The quantity of the improvement can be estimated by Amdahl's law. It gives the speedup which can be obtained as a result of the change. The speedup is defined as follows [PH02, Ch.1.6]:

$$Speedup = \frac{Execution\ time\ for\ an\ entire\ task\ without\ using\ the\ enhancement}{Execution\ time\ for\ an\ entire\ task\ using\ the\ enhancement\ when\ possible}$$

A speedup tells how much faster the computer is with the enhancement than without it. A speedup depends on two factors:

- $fraction \le 1$ . The fraction of the computing the enhancement applies.

- $improvement \ge 1$ . The increment in computing power when the enhancement was effective the whole processing time.

The new execution time constitutes of the fraction of the old execution time the enhancement is not effective and of the fraction of the new execution time which is affected by the enhancement. Formally [PH02]:

$$Execution \ time_{new} = Execution \ time_{old} * ((1 - fraction) + \frac{fraction}{improvement})$$

The speedup can be resolved from the equation:

$$Speedup = \frac{Execution \ time_{old}}{Execution \ time_{new}}$$

Assume a computer including an L1 cache only. The fraction of L1-cache hits in the machine is (only) 35%. Each single, non-sequential memory access in the computer lasts 45ns on average. Adding an L2 cache would reduce the data-access time by 25% on the average by decreasing the number of (L1 and L2) cache misses. In a similar machine including an L2 cache, the average fraction of L2 hits is 92%. Therefore the hypothetic L2 cache has impact at most on  $\frac{(100\%-35\%)*92\%}{100} \approx 60\%$  of all memory references. By using Amdalh's law, it is possible to estimate the speedup originated in the existence of L2. In the example machine the speedup is calculated as follows:

Execution time\_{new} =

$$45ns * \left(\frac{100\% - 60\%}{100} + \frac{0.6}{1.25}\right) = 39.6ns$$

and

$$Speedup = \frac{45ns}{39.6ns} \approx 1.136$$

By adding L2-cache memory to the example computer, memory references became nearly 14% faster. If memory access is the main performance bottleneck, the calculated speedup applies directly to the program performance. That is, running the program on the example computer would be about 14% faster with an L2 cache than without it.

Amdahl's law demonstrates that each particular improvement affects only to a certain portion of computing. A technological gain depends on how widely new technology can replace the old and inefficient solutions. According to Amdahl's law, the use of enhanced parts of the computer should be maximized if the performance is the goal. Similarly, the hardware development should be focused on those parts whose fraction of total computing time is biggest.

Normally executing a program stresses both the CPU and the memory. Based on the knowledge about the current hardware development trend and Amdahl's law, it is justified to suppose that moving the stress more on the CPU will make the program faster.

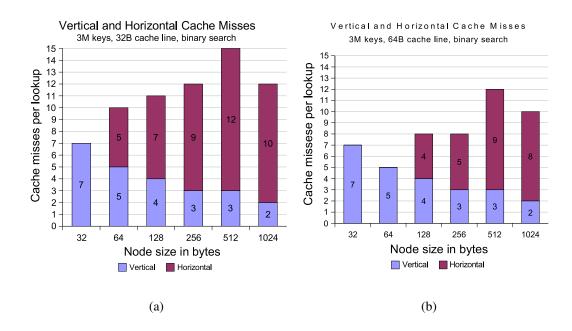

# 3.2 Enhancing data locality of an index node

The number of main memory references can be decreased by increasing the cache hit rate. In that sense, locality is one of the most effective properties of a program. To benefit from spatial locality, concurrently or consecutively accessed data should be located into memory within the same cache line. If the data exceeds the size of the cache line, contiguous cache lines should be used. This reduces the number of memory accesses and also the number of cache misses. In a B<sup>+</sup>-tree, keys are stored into nodes. When a key is read, with a high probability the next bigger key is to be read soon. If the next key lies in the same cache line, reading it does not result in an additional cache miss. Therefore, the B<sup>+</sup>-tree benefits from the spatial locality due to its data access pattern. Spatial locality, however, can be enhanced by compressing both the node structure and the information the node includes.

The compression of node structure is achieved in CSS- and CSB<sup>+</sup>-trees [RR99, RR00]. Both structures, however, include many other enhancements in addition to the pointer elimination and the effect of pointer elimination alone is hard to isolate from the results. Therefore the pointer elimination is further investigated here by looking its impact on the number of nodes needed and on the efficiency of the node search (Subsection 3.2.1). Compressing the node information relates to the general problem of compressing integers so that the order is retained. One such compression method is defined and evaluated in Subsections 3.2.2 and 3.2.3, respectively.

Figure 6: A traditional B<sup>+</sup>-tree in which half of the node is filled with pointers.

Figure 7: A CSB<sup>+</sup>-tree in which the node fan-out is increased by removing unnecessary pointers and storing additional key values instead.

### 3.2.1 Compressing pointer structures

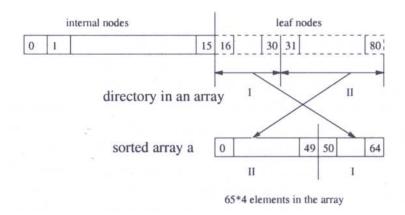

A cache line is relatively small compared to a memory page. The size of a memory page is typically 4–16KB. The size difference emphasizes the need for using economical data storage conventions in main-memory databases. Nodes of a classic B<sup>+</sup>-tree include [key value, pointer]-pairs, as shown in Figure 6. With a 32-bit address space, 4-byte key values and 32-bytes-wide cache lines, there is space for at most 4 keys and their pointers in one node, if the size of a node is restricted to that of a single cache line. The height of a tree using such nodes would be about  $log_4n$  with n keys. For  $n=1\ 000\ 000$  the height would be 10. If the number of keys could be doubled, the height of a tree would be reduced to  $log_8n=7$ . In large structures, where reading a node close to the leaf level is likely to cause a cache miss, the difference of three in height may be significant.

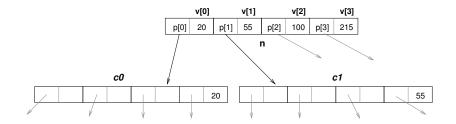

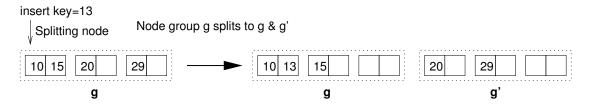

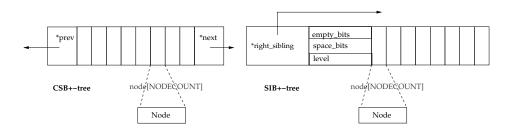

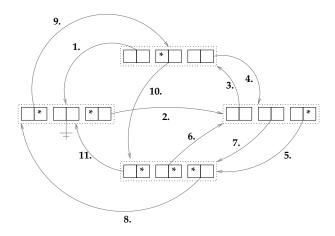

Let us assume that a  $B^+$ -tree node n consists of k key values (v) and k pointers (p). The number of keys in one node can nearly be doubled by removing most of the pointers. Only one pointer needs to be left for each node, as shown in Figure 7. The space freed is used for storing additional key values. The compressed node structure, called CC-node, is used in the  $CSB^+$ -tree [RR00].

In pointer removal the child nodes c[0] - c[k-1] pointed to by the pointers p[0] - p[k-1] are copied to a contiguous memory area g, which is called a *node group*. The pointer p[0] is set to point to the beginning of the node group g.

During the tree-traversal of this compressed structure the right child node is located as follows:

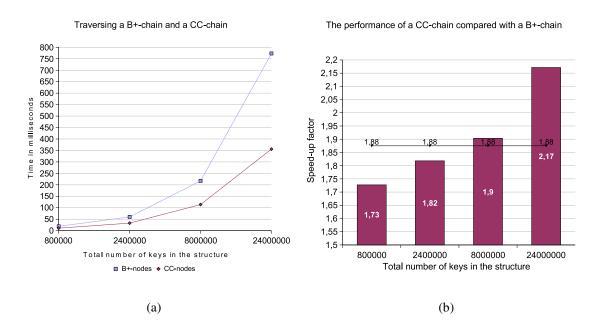

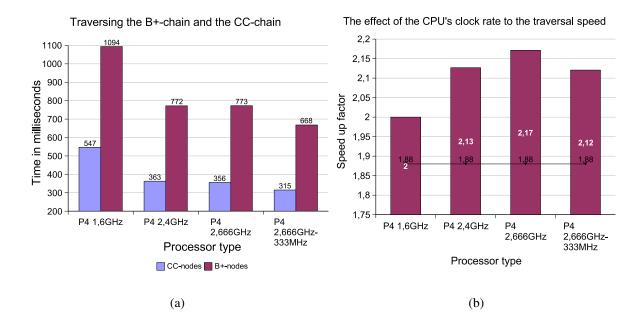

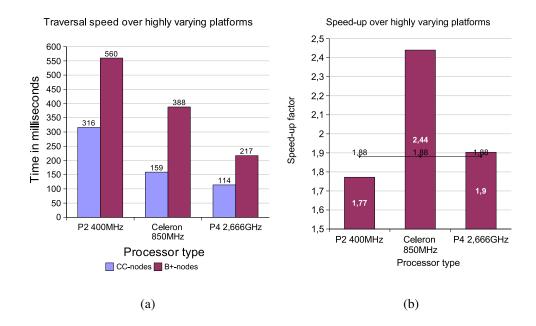

Assume that two linked lists called a B<sup>+</sup>-chain and a CC-chain are built from set of B<sup>+</sup>-nodes and CC-nodes, respectively. Both chains have one node representing the root. The other nodes are linked to each other by child pointers (see Figures 27 and 28 in Section 7.2) each node having exactly one child node. Both structures are entirely filled with keys and pointers. The use of compressed CC-nodes results in a less memory consuming structure in which, however, the search within a CC-node requires more comparisons than in B<sup>+</sup>-node. For any  $x \ge 4$  a B<sup>+</sup>-chain uses l times the amount of memory used by the corresponding CC-chain. The value of l is calculated as follows:

$$l = \frac{\frac{x}{2} + 1}{x - 1}$$

The impact of the pointer compression on the search efficiency can be evaluated by storing some large number of keys into the chains, traversing them through and by comparing the time spent. During the traversal each node is accessed only once. Therefore the test causes at least one cache miss every time a node is accessed thus emphasizing the influence the data locality and the size of the structure has on the traverse speed. This is not the case when a corresponding tree structures are traversed since the nodes on the uppermost levels of the trees are practically always already in the cache. Therefore accessing a node rarely causes a cache miss during a tree traversal.

The smaller size of the CC-chain causes less cache misses. The increased probability of two items being in the same memory page reduces the possibility for TLB-misses while traversing the CC-chain. The smaller size of the CC-chain also reduces the amount of memory the structure needs. Since in the CC-chain adjacent nodes are in contiguous memory space, reading successive nodes becomes a little faster due to the avoidance of translating the pointer addresses. On the other hand, an additional calculation must be done in order to resolve the right child node from the child node group. Since the solution is an array in its nature, updating the structure is more expensive than updating similar pointer structure. Both the B<sup>+</sup>-chain and the CC-chain were implemented by the author in order to evaluate the possible performance benefits resulting from the pointer elimination (see Chapter 7). The search speed of the chains were tested by creating chains including

varying number of key values and traversing them through. The tests are documented in Section 7.2.

### 3.2.2 An order-preserving compression method for numeric values

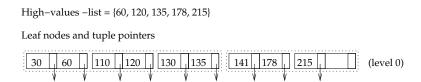

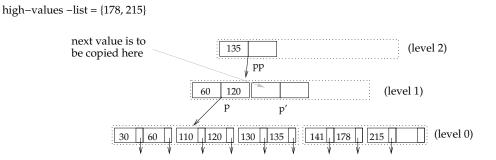

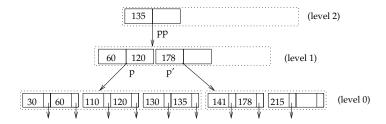

In many cases the keys to be inserted to an index are numeric, such as 32-bit integers. Depending on the numbering scheme, of course, the indexed values are likely to lie more or less close to each other. If the difference between the biggest key, the *high value* of a node, and the other keys in the same node can be represented by using one or two bytes, it would be beneficial to represent only the *difference values* between the keys instead of storing the actual values into the node. The method is called the *difference compression* hereafter.

Assume that the key values are 32-bit integers and that there are n keys (k[0,...,n-1]) in a node. By using the difference compression only the high value (k[n-1]) is presented "as is". The other key values k[0,...,n-2] are represented by difference values d[0,...,n-2] so that

$$d[x] = k[n-1] - k[x], \ 0 \le x \le n-2$$

Difference values are expressed on 1,2 or 4 bytes, that is, 8, 16 or 32 bits, respectively. Let number(y) be a function which returns the number of key values in a node which are expressed by y bytes. Let space(x) be a function which returns the minimal number of bytes needed in expressing the value x. The function is defined by the equation:

$$space(x) = \lceil \frac{log_2 x}{8} \rceil$$

The difference values d[0,...,n-2] are ordered, so that k[n-1] > d[0] > ... > d[n-2] and  $space(k[n-1]) \ge space(d[0]) \ge ... \ge space(d[n-2])$ . Because a node can include difference values with different sizes, the number of keys of each size must be stored in nodes. For that reason, each node includes fields a, b and c with a = number(4), b = number(2), c = number(1). In other words, the value of a includes the number of key values in the node, which are represented by 4 bytes. If other key values exist in the same node, a gives the offset to the first key value which is represented by less than 4 bytes. Similarly the values of a and a include the number of key values represented by 2 bytes and by 1 byte, respectively.

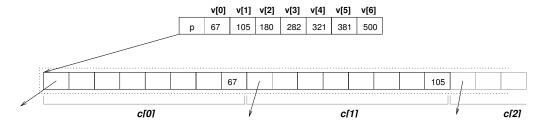

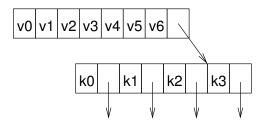

The search of a key s within a node starts by calculating a difference value t = k[n-1] - s. The search is restricted to those difference values d[x] for which the condition space(d[x]) = space(t) holds. The search among the relevant difference values may be accomplished either by binary or sequential search. An example of a node which is organized by using the difference compression method is depicted in Figure 8. The pseudocode for a search from a compressed node is presented in Appendix 2.

Let x be the number of unused bytes in the node and i the size of keys being inserted. In order to estimate the memory consumption of the difference compression method an

Figure 8: An index node which is filled with one full key value, difference values and counters of occurrences of each key-size.

average difference d between any two subsequent keys must be assumed. The memory consumption of the difference method for storing a given set of keys can be calculated by using the following algorithm:

$$f(x,i) = \begin{cases} a + f(x - a * i, i + 1) & \text{if } x \ge i \\ 0 & \text{if } x < i \end{cases}$$

Here

$$a = \min \left\{ x \; div \; i, \; (2^{8*i} - 1) \; div \; d \right\}$$

The execution of the algorithm begins by initializing the arguments as follows:

x =number of bytes available for keys in the node,

i = the size of key-values to be inserted at this round,

d = the difference between any two subsequent key-values.

As an example, assume a 64-byte node. The high value reserves 4 bytes thus leaving 60 bytes for keys and offset values. Three offset values require 3 bytes, so keys have 57 bytes. Key values are integers and, in theory, lie between  $[1..\infty[$  and they are inserted in ascending order. In this example the difference of any consecutive key values, the value of d, is assumed to be 64. In the first round, the key size is 1. Thus, we have:

$$x = 57,$$

$i = 1,$

$d = 64.$

The calculation begins by determining the a. If the difference between the high value and the 57th key is smaller than or equal to 255 (which is the biggest value which can be expressed by a single byte), we choose  $a = 57 \ div \ 1 = 57$ . In this example the difference between the high value and the 57th key is 64\*57 = 3648. Therefore only the biggest 3 key values (= 3 smallest difference values) can be stored by using only a single byte. So, in the first round, a = 4. That means that four keys can be stored into the node by using 1

byte. 53 bytes will be left for other difference values. The whole calculation proceeds as follows:

$$a = \min(57 \ div \ 1, (2^8 - 1) \ div \ 64) = 255 \ div \ 64 = 3$$

$$\Rightarrow f(57, 1) = 3 + f(54, 2)$$

$$a = \min(54 \ div \ 2, (2^{16} - 1) \ div \ 64) = 54 \ div \ 2 = 27$$

$$\Rightarrow f(54, 2) = 27 + f(54 - 27 * 2, 3) = 27 + f(0, 3) = 27$$

$$3 + 27 = 30$$

As a result, 30 compressed keys and the high value can be stored into each node. Three difference values out of 30 are expressed by a single byte and 27 difference values by 2 bytes.

### 3.2.3 Comparing uncompressed and compressed node structures

Assume a data structure in which integer keys are stored into 32-byte nodes. Besides keys, there is a 4-byte pointer in each node which points at the first child node and makes traversing the structure possible. Keys are, by default, 4-byte integers stored into nodes in ascending order. Each node can include at most 7 keys in addition to the child-pointer. Such a structure is called an *uncompressed list*. To enhance the spatial locality of nodes, keys could be compressed by using the difference method (Subsection 3.2.2). By this way the number of keys which can be stored on a 32-byte node varies between 6 and 21. The structure consisting of such compressed nodes is called a *compressed list*. Storing keys into the uncompressed list is space-inefficient but it makes the processing of the nodes simple. Therefore, this method should intuitively be efficient in a computer with relatively fast memory and relatively slow processor. The compressed list consumes less memory than the uncompressed list, but inspecting a compressed node necessitates more processing power from the CPU. Thus, using compressed lists should work well with a computer with high memory latency and an efficient processor.

The difference in memory consumption between uncompressed and compressed lists is notable. Assume that the maximum difference between any two consequtive keys is 64. A compressed node can include at least 13 keys if the difference method is used. That is 1.86 times more that can be stored into an uncompressed node. As a consequence, the uncompressed list including the same amount of keys consumes at least 1.86 times more memory than the compressed list.

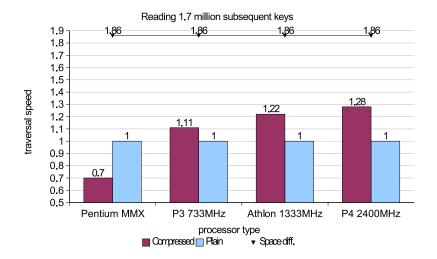

The read-access times of the structures was tested with four computers. The structures were filled with approximately 1.7 million keys. Keys were stored into 32-byte nodes in ascending order. Structures were traversed 1000 times and the average read-through time

| CPU                            | Bogomips |

|--------------------------------|----------|

| i586 Intel Pentium MMX 233 MHz | 460.92   |

| i586 Intel Pentium III 733 MHz | 1458.17  |

| i686 AMD Athlon 1333 MHz       | 2660.76  |

| i786 Intel Pentium 4 2400 MHz  | 4784.12  |

Table 1: CPUs used in traversal test (see Figure 9) and related bogomips.

was calculated for each computer. Distinctly exceptional values, such as those originating from disk accesses or context switches, were discarded. Before each traversal it was assured that the cache was cold, that is, the cache did not contain any of the data to be read.

Most of the modern processors have a branch-prediction property [PH02, Ch.3.4], which enables prefetching data from the memory before it is actually referenced. This is a powerful mechanism, which efficiently can hide the memory latency. Therefore, it had to be disabled in order to create an illusion of a realistic index-traversal situation. The hypothetic prefetch mechanism was effectively disabled by surrounding each read operation by a dummy if-clause. The meaning of the if-clauses were to offer 6 to 21 possible paths to proceed after the current node. This corresponds to an index-search operation where an inner node is inspected in order to determine the right child node on a lower level.

Figure 9 shows the measured behaviour. It also verifies the intuition to be discussed in the end of Section 3.1. The traversal time of the uncompressed list is normalized to 1 in the chart in Figure 9. Another bar represents the relative speed of traversing the compressed list. The speed of traversing the compressed list is calculated as follows:

$$speed of traversing the compressed list = \frac{traversal time of the uncompressed list}{traversal time of the compressed list}$$

The curve shows the relative difference between the sizes of uncompressed and compressed lists. The curve having consistent value 1.86 shows how much faster the traversing of compressed lists was if reading nodes of both lists would require an equal amount of processing.

As expected, the computer with a relatively fast memory and a slow processor reads uncompressed nodes faster even though the number of nodes read is nearly twice the number of compressed nodes. As the clock rate of the CPU increases and the relative speed of memory decreases, reading compressed nodes becomes faster. The fastest machine, Pentium 4 (Tables 1 and 4 on pages 23 and 56 respectively), reads the structure with compressed nodes over 28% faster than the uncompressed list.

Figure 9: Traversing compressed and uncompressed data structures by four different computers.

# 3.3 Avoiding conflict misses by relocating data

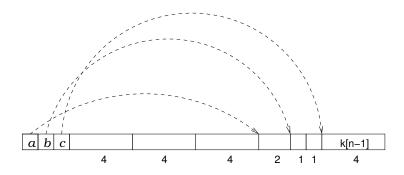

Cache memory consists of sets (recall Subsection 2.5.1) whose size and number is related to cache associativity. For instance, in a 4-way-associative cache, each set includes four cache lines. Each set is actually a list with some item selection method, such as FIFO, LRU or MRU. Recall the relation between cache size, cache line size and associativity. Given a 4-way associative cache 16KB in size with 32B line size. According to the formulas in Subsection 2.5, the cache consists of  $\frac{16kB}{32B} = 512$  cache lines and  $\frac{512}{4} = 128$  sets. Depending on its address, data in main memory may be mapped to 128 different sets in cache. Sensitive data arrangement tries to locate hot data items in such a way that they do not compete against each others about same cache sets.

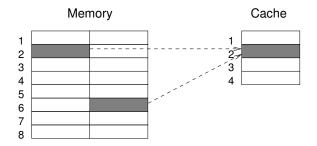

In pointer-based data structures data is located randomly into memory. For dynamic lists, for instance, memory is allocated on-demand. That is, memory is allocated during the insertion of the item. As a consequence there is no guarantee about the cache mapping and if successively accessed data items will be mapped to the same slot in cache. Items that map to the same cache set may conflict (see Figure 10). With a direct-associative cache ("1-way-associative"), reading such items repeatedly, one after another, always causes a cache miss. In the worst case, two successive items are located into different memory pages, which may, in addition to unnecessary cache misses, raise additional TLB-misses. Thus, storing data items carefully may result in a notable impact on the performance of the program.

Data items equal in size with a cache line can be located so that concurrently accessed items will not conflict in cache. Items are colored according to their access rate. In a two-color scheme the cache is divided into two parts, one for items of each color. Hot items are separated from cold ones so that rarely accessed items will not replace hot items

Figure 10: Two memory blocks conflicting in cache.

in the cache. Often accessed items are distributed evenly into "hot areas" so that conflicts among hot items will be minimized [CHL99].

# 3.4 Reducing compulsory misses via prefetching

Many processors offer means for loading data beforehand to the CPU before it is needed. Prefetching means reading data from memory into the cache in parallel with other computation before an actual cache miss occurs. Non-blocking caches are required so that multiple cache accesses may be overlapped. Prefetching reduces the effect of memory latency caused by cache misses. Prefetching can be done either by hardware or by software. Here software prefetching is emphasized. It can further be divided into hand-inserted (= explicit) prefetching and compiler-assisted prefetching [Met97].

Prefetching is especially interesting in the context of data structures. Many compilers, like GNU gcc, offer library functions to perform an explicit prefetching. Using them may notably decrease the number of compulsory misses. Compilers can typically investigate loops, find a suitable distance for prefetch commands and insert them automatically to the binary code. This makes traversing large arrays faster. Prefetching increases the degree of the concurrency of computation in uniprocessor computers. However, careless usage of explicit prefetching can also produce an increased number of conflict misses if prefetched data items conflict with other concurrently accessed data items.

When supported by a compiler, prefetching commands can be added by hand into suitable locations in program code. When met during the execution, prefetch commands launch copying the data from a particular memory address into the cache. As a consequence, the prefetched data arrives to the cache, hopefully before a cache miss is detected. If the prefetch succeeds, the memory latency can be alleviated. If data comes to the cache too early, it may be removed from the cache before it is needed.

The use of prefetch applies well to array-based structures but not that well to pointer-based structures. The location of items of an array is known during compilation. Therefore, the prefetch commands can be added during compilation. The location of the items of a linked list, however, is known only one step ahead. Thus, only the next item can be prefetched

before it is referenced. It is likely that one-step lead is not enough and that the CPU must wait for the data even it was prefetched. This problem can be alleviated by using "jump pointers". In addition to "next pointer", each item has an additional jump pointer to some item ahead. This enables prefetching items further than one step ahead but makes the structure updates trickier [CGM01]. Selecting an optimal read-ahead distance is crucial but when successful, the memory latency may nearly be hidden by concurrent prefetching [CB92, Met97].

In cache-conscious indices the node size is small, usually equal to cache-line size or its (small) multiplier. Usage of small nodes reduces cache misses originating from within one single node. Small nodes, however, produce higher tree structures, thus increasing cache misses during the traversal. An optimal solution seems to be a low structure with nodes that can be read without extra memory latency.

Prefetching suits well to B-tree algorithms. Nodes larger than a cache line can be prefetched immediately when the read of the node starts. Scanning the leaves of a  $B^+$ -tree is similar to a linked list. With explicit prefetch, over 90% of arising memory latency can be hidden. In general, prefetching may be adapted to B-tree algorithms as follows [CGM01]:

- Search within a node: every cache line but the first is prefetched at the beginning of the search.

- Insert: when a node splits, new node and the splitting node are prefetched before the key distribution.

- Delete: keys of the sibling of a deleted node must sometimes be re-distributed. Therefore, the sibling of a deleted node is prefetched during the search phase.

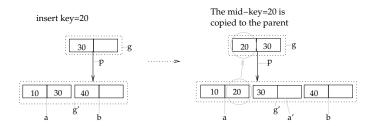

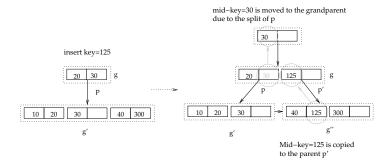

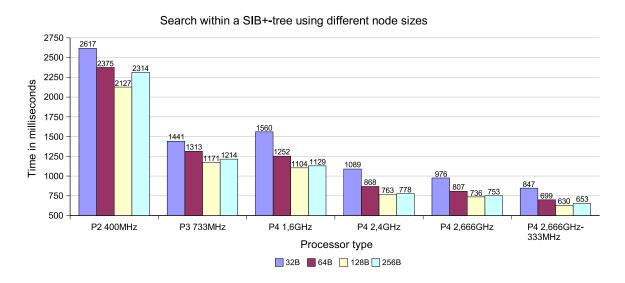

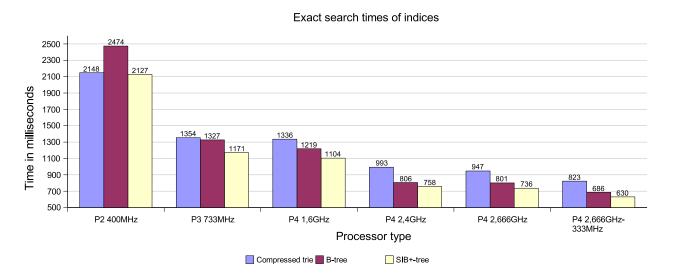

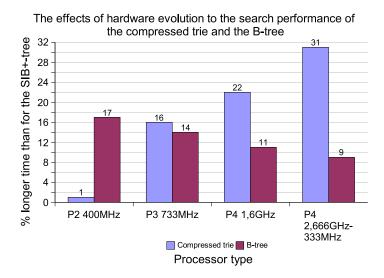

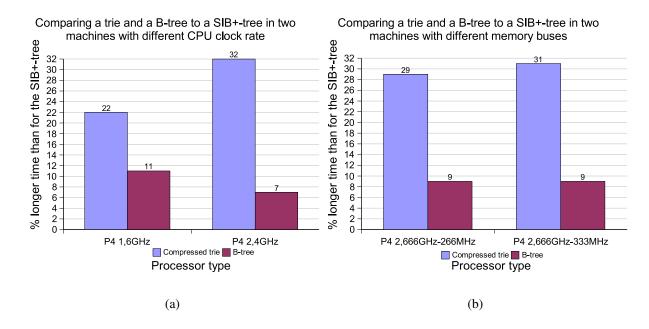

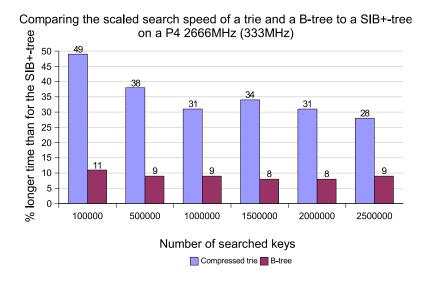

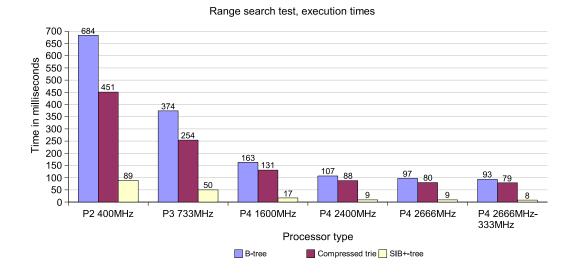

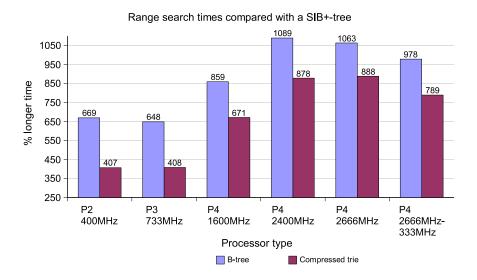

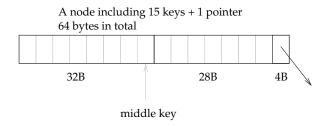

Prefetching applies also to bulk-loading of B<sup>+</sup>-trees [CGM01].